在Android 10之前

可以用

dumpsys window windows | grep mCurrentFocus

或者

dumpsys activity activities | grep mResumedActivity

在Android 10之后,需要使用

dumpsys window displays | grep mCurrentFocus

dumpsys window displays | grep ‘mFocusedApp’

在Android 10之前

可以用

dumpsys window windows | grep mCurrentFocus

或者

dumpsys activity activities | grep mResumedActivity

在Android 10之后,需要使用

dumpsys window displays | grep mCurrentFocus

dumpsys window displays | grep ‘mFocusedApp’

https://github.com/fgsect/scat ( Signaling Collection and Analysis Tool)

安装pyUSB和pySerial

apt install python3-usb python3-serial

在手机上暴露diag端口(跟使用qxdm一样)

setprop sys.usb.config diag,adb

建议直接使用usb接口来使用SCAT

lsusb ... Bus 001 Device 033: ID 05c6:901d Qualcomm, Inc. ...

可以看到 总线1,设备33是 我们开了diag端口的手机

安装和运行

git clone https://github.com/fgsect/scat cd scat ./scat.py -t qc -u -a 001:033 -i 0

参数解释:

-t qc 高通芯片的手机

-u 直接使用usb协议,而不是串口

-a 001:033 指定usb设备地址,1号总线,33号设备,用lsusb命令可以看到这些信息

-i 0 因为是usb复合设备,根据我们上面的设置,0是diag, 1是adb. 这个应该根据不同手机开启diag的情况调整

默认情况下,SCAT将手机到的包发给127.0.0.1 (可以通过 -H 指定发送的地址)

控制平面的包,以GAMTAP协议,发送到UDP端口4729

用户平面的包,以IP协议,发送到UDP端口47290

wireshark选中 loopback设备, 过滤条件 为 port 4729 and udp

依赖于 pyserial和crcmod apt install python3-serial python3-crcmod 协议解析和加密解密算法库 git clone git@github.com:P1sec/pycrate.git cd pycrate python3 setup.py build cd .. QCSuper字节 git clone git@github.com:P1sec/QCSuper.git qcsuper cd qcsuper mv ../pycrate/build/lib/pycrate_* ./ 运行 ./qcsuper.py --adb --decrypt-nas --pcap-dump /dev/shm/1.pcap

在Oneplus 5T上测试通过

在Redmi 7上不能捕获数据

用Wireshark打开1.pcap,即可进行分析

不能正常运行的手机,可能是

inputs/external/adb/adb_linux

或

inputs/adb_bridge/adb_bridge

的问题

cd inputs/adb_bridge/adb_bridge

make CC=/Android/Sdk/ndk/21.3.6528147/toolchains/llvm/prebuilt/linux-x86_64/bin/aarch64-linux-android21-clang

/Android/Sdk/ndk/21.3.6528147/toolchains/llvm/prebuilt/linux-x86_64/bin/aarch64-linux-android21-clang adb_bridge.c -std=c99 -Werror -fPIE -pie -o adb_bridge

开启手机的diag模式

setprop sys.usb.config diag,adb 有些型号需要设置成 setprop diag,serial_cdev,rmnet,adb 不然diag模式不正常

将手机日志modem文件转换成pcap文件:使用QCAT打开isf文件,菜单选择Tools,Convert Log to PCAP/TXT

GMM== GPRS Mobility Management

MM== Mobility Management

EMM== EPS (Evolved Packet System) Mobility Management

在QXDM按F12,或者从菜单选择 View->Common->Filtered View

打开Filtered View之后, 打开右键菜单,选择Config

左侧Item Types选中 Log Packets (OTA), 右侧 选中我们关心的 UMTS, GSM, Lte, WCDMA类型

名称:LTE NAS EMM Plain OTA Outgoing Message 消息类型: Attach request Msg

Authentication request

Authentication response

ESM information request

ESM information response

Attach accept

Attach Complete

EMM information

PDN Connectivity request

Activate default EPS bearer context request

Activate default EPS bearer context accept

Attach request

Authentication request

Authentication response

Security mode command

Security mode complete

Attach reject

GSM_MOB_MANAGEMENT中的 MM/Location Updating Request, 方向 MS to Network

GSM_GMM_Message中的 GMM_Attach_request 方向 : MS to Network

GSM_MOB_Management中的Authentication Request 方向:Network to MS

GSM_GMM_Message中的GMM Authenticaiton and ciphering request

MM/Authentication response

MM/TMSI Reallocation Command

MM/TMSI reallocatin Complete

GMM/Authentication ANd Ciphering Response

MM/Identity Request

MM/Identity Response

GMM/Attach reject

通信模组需企业自行采购。使用vSIM和eSIM卡和通信模组有依赖关系,全球SIM联接适配的通信模组型号如下,如不在下列型号范围内,可线下联系华为接口人咨询。

模组型号 固件版本 支持SIM卡类型

移远EC20 CEFASG vSIM+传统实体卡

EC20 CEFASG EC20CEFASGR08A01M2G_HW eSIM+传统实体卡

EC20 CEHDLG EC20CEHDLGR06A01M1G_HW eSIM+vSIM+传统实体卡

EC25 EFA EC25EFAR06A01M4G_OCL_01.001.01.001 eSIM+传统实体卡

有方 N720-CA-61S2 eSIM+传统实体卡

N720PCIE-NA-CA-61S2 eSIM+传统实体卡

广和通 NL668 eSIM+传统实体卡

域格CLM920 NC5 eSIM+传统实体卡

vSIM即virtual-SIM,虚拟SIM卡技术。特指没有实体SIM卡,完全靠通信模块自身软硬件实现通信的方式。拥有vSIM功能的通信模块,配合为vSIM特殊定制的底层软件,实现了内置加密存储数据(IMSI、KI等)。在登陆网络、鉴权、通信时,自动处理相应的逻辑,从而实现不需要实体SIM卡也能提供稳定的通信体验。全球SIM联接云服务提供vSIM类型的连接服务,客户的设备不需要实体卡,直接使用内置支持vSIM技术软件的通信模组就可以连接上网,且拥有比实体卡更灵活的功能,支持选择全球SIM联接服务提供的全球移动网络流量。全球SIM联接服务根据客户提供模组的IMEI和连接服务套餐配置码号资源,当客户使用该模组的设备上电启动,自动从全球SIM联接服务下载对应的码号并启用联网功能。

eSIM即嵌入式SIM(embedded UICC,也称eUICC)的缩写,顾名思义,与传统可插拔的SIM卡不同,eSIM的概念是将SIM卡直接嵌入到设备中。所以,eSIM可以最终让SIM卡槽消失,让设备拥有更轻薄的机身和更高的可靠性。而因为SIM卡功能的虚拟化和设备集成化,SIM卡码号的切换也将迎来全新的用户体验:用户不必再来回插拔传统SIM卡,而是直接通过与终端交互,通过APP或者云端,即可在全球范围内将终端智能设备连接到所选择的当地网络,且可动态切换,使设备可以始终处于优质网速中。通过这种方式,eSIM不但增强了整体用户体验,也为设备的管理分配带来极大便利。

AT+HWSIM 功能:用于关闭或者使能ESIM/VUICC功能。

AT+HWSIM=enable

+HWSIM OK

AT+HWSIM=disable

AT+HWICCIDLIST 功能:读取使用的ESIM卡内部ICCID列表,将所有的ICCID以及其类型和状态展示,num表示读取的卡的个数,按照[iccid, type,status]将信息展示出来

code定义:1、读取失败;2、ESIM不识别;3、不支持该功能;4、位置错误;

type定义:1、种子卡;2、业务卡;3、未知;

status定义:0、disable;1、enable;2、未知。

AT+HWICCIDENABLE=ICCID

AT+HWEID

功能:用于获取当前的ESIM卡的EID

获取到了eSIM卡(电子卡文件,非实体卡)。请确保固件支持eSIM卡并且模组没有eSIM存在。通过AT+QCFG?命令以及AT+QESIM=LIST命令确认模组内部没有实体卡。

AT+QESIM=LIST

AT+QESIM=CID

AT+QESIM=ICCID

eSIM卡文件长度为2504字节

AT+QESIMWRITE=length,timeout 命令来写种子卡,如20秒内写入种子卡,则命令为:AT+QESIMWRITE=2504,20

支持 32 路中断请求输入

每路输入可配置是否使能,每一路中断输入可配置为 FIQ 或 IRQ

具有一个 FIQ 通道,为了使处理速度最快,务必使只有一个通道设置为 FIQ,优先级最高

具有 32 个 IRQ 通道,每个通路可配置选择哪路中断源输入

32 个通道分为 8 个不同的优先级,

通道 0—3 具有最高的优先级,通道 4—7 具有次高的优先级,依次类推,通道 28—31

具有最低的优先级

相同优先级的 4 个通道之间不能相互打断;

如果同时产生相同优先级的几个通道的中断(比如通道 0—3),会优先执行低通道中断(先执行通道 0,然后通道 1,然后通道 2,最后通道 3)。

中断向量在ARM7处理器中位于0到0x1C地址

为了在不同的操作模式下对中断的替换使用,一小片的Boot块和SRAM空间,需要重新映射。中断向量的重映射是通过内存映射控制特性完成的。

| 模式 | 激活条件 | 用途 |

| boot loader | 通过任何复位操作硬件激活 | 在复位后,boot loader总是被执行。启动块的中断向量被映射到0地址,在boot期间处理异常和使用中断。 |

| Flash模式 | 通过boot代码,软件激活 | 在Flash中的有效的用户程序签名被识别出来,且不强制执行boot操作时,就会激活,启动用户程序。中断向量没有重新映射,还是处于Flash的0地址 |

| RAM模式 | 通过用户程序,软件激活 | 由用户程序激活。中断向量被映射到SRAM的底部 |

有些SOC的Boot Block是Boot ROM,

另外一些,还是Flash, 只不过是从整体的Flash重新映射一部到boot block地址空间,比如 LPC213x, BOOT BLOCK(12 kB REMAPPED FROM ON-CHIP FLASH MEMORY) 从0x7FFF D000到0x8000 0000

当一个软件中断(SWI)生成时, ARM内核 总是会从 0x8地址取得一个32位宽的数据。 这意味着, 当MEMMAP[1:0]=10 (RAM模式), 数据实际是由

0x4000 0008地址提供的。 当MEMMAP[1:0]=00 (boot loader模式), 数据由 0x7FFF E008 地址 提供(从芯片上的bootloader映射的boot block)

The flash boot loader code is executed every time the part is powered on or reset. The

loader can execute the ISP command handler or the user application code.

The boot block is 12 kB in size and resides in the top portion (starting from 0x0007 D000) of the on-chip flash memory.

After any reset the entire boot block is also mapped to the top of the on-chip memory space i.e. the boot block is also visible in the memory region starting from the address 0x7FFF D000.

The flash boot loader is designed to run from this memory area but both the ISP and IAP software use parts of the on-chip RAM. The interrupt vectors residing in the boot block of the on-chip flash memory also become active after reset, i.e., the bottom 64 bytes of the boot block are also visible in the memory region starting from the address 0x0000 0000. The reset vector contains a jump instruction to the entry point of the flash boot loader software.

The boot block is present at addresses 0x0007 D000 to 0x0007 FFFF in all devices. ISP and IAP commands do not allow write/erase/go operation on the boot block.

启动块是不能被擦除的

LPC213x Bootloader(启动装载程序)控制复位后的初始化操作,并提供Flash ISP编程接口。它驻留在Flash的最前面的12KB,只能读不能写

Memory分为ROM, RAM, Flash三种

ROM起始地址 0, 大小 8K

也就是从 0到0x2000

从 0x2000 0000开始,也能访问到ROM

RAM 起始地址 0x0800 0000

0x800 0000 到 0x800 4000, 大小16K

Flash(NorFlash) 起始地址 0x00000000 – 0x03FFFFFF 64M空间,

实际大小0x89000 (548K)

NORFLASH 起始地址为 0x20000000

地址重映射寄存器

SCREMAP 0X30000034 地址重映射寄存器

Flash读写

FLCON0

000 读

001 对一行进行编程

101 擦除一行

110 擦除一页

FLSTS 操作状态

IO管脚复用选择寄存器

FUN_SEL 0X30000044

位 名称 读写 功能 0 gpio_spi_sel r/w 0=gpio, 1=spi_m 1 保留 2 iso7816_gpio_sel r/w 0=7816 slave, 1=gpio 4:3 jtag_gpio_sel r/w 00=jtag, 01=jtag, 10=gpio, 11=spi_s 6:5 gpio_uart_sel r/w 00=gpio,01=gpio, 10=uart, 11=7816 master

首先,选择是传统的寄存器控制,还是增强型控制(增强型,用的CPU本地总线,速度更快)

System Control and Status flags register (SCS)

其中 GPIO0M位 = 0, 表示GPIO 端口0通过传统的APB地址控制寄存器

= 1, 表示GPIO 端口0,高速控制

复位后, GPIO0M =0, 通过APB地址控制

传统的APB访问寄存器有:

IOPIN= 当前的GPIO值

IOSET= 输出设置寄存器,控制输出引脚的状态。写1在对应的引脚产生高电平。

写0,没影响。

IODIR= 方向控制寄存器。决定是输入,还是输出。

IOCLR= 输出清除寄存器。控制输出引脚的状态。写1在对应引脚产生低电平,并且会

清除IOSET寄存器中的对应位。写0,没有影响。

高速端口访问

FIODIR = 快速GPIOS端口方向控制寄存器。

FIOMASK = 掩码寄存器

FIOPIN = 快速GPIO引脚值寄存器。

FIOSET =

FIOCLR =

PINSEL0 功能选择寄存器

配置 端口0的P0.0到P0.15引脚功能

bit1-bit0 = 00 表示 P0.0 的引脚为 GPIO

01 为 UART0的TXD

10 为 PWM1

11 保留

PINSEL0在系统复位后为 0

PINSEL1 配置 端口0 的P0.16到P0.31引脚

初始化并行输入输出(PIO)控制器

注意,在每个PIO引脚,都有个独立的内部上拉电阻. 这些上拉电阻默认都是启用的。因为它们在点亮LED上没有用。所以,应该被关掉,以减少电量消耗。可以通过PUDR(Pull Up Disable Register)来关掉。

#include "AT91SAM7S256.h" #define LED_A (1U<<0) // PA0, pin 48 #define LED_B (1U<<1) // PA1, pin 47 /* Configure the pins as outputs */ AT91C_BASE_PIOA->PIO_OER = (LED_A | LED_B); /* Enable PIOC control on the pins*/ AT91C_BASE_PIOA->PIO_PER = (LED_A | LED_B); /* Disable pull-ups */ AT91C_BASE_PIOA->PIO_PPUDR = (LED_A | LED_B); /* Turn LED on, high level */ AT91C_BASE_PIOA->PIO_SODR = LED_A; /* Turn LED off, low level */ AT91C_BASE_PIOA->PIO_CODR = LED_A;

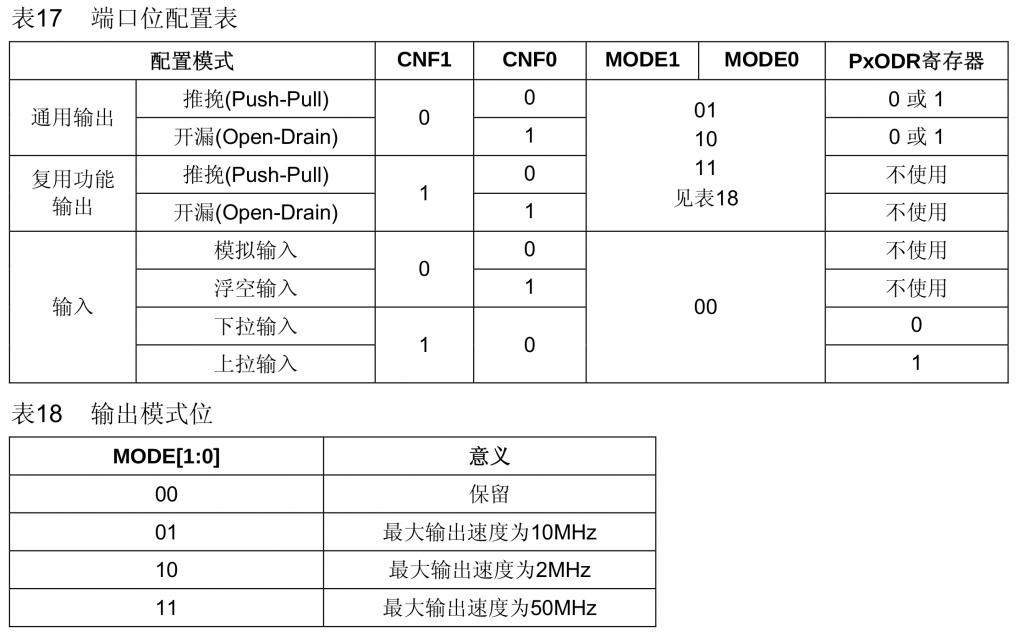

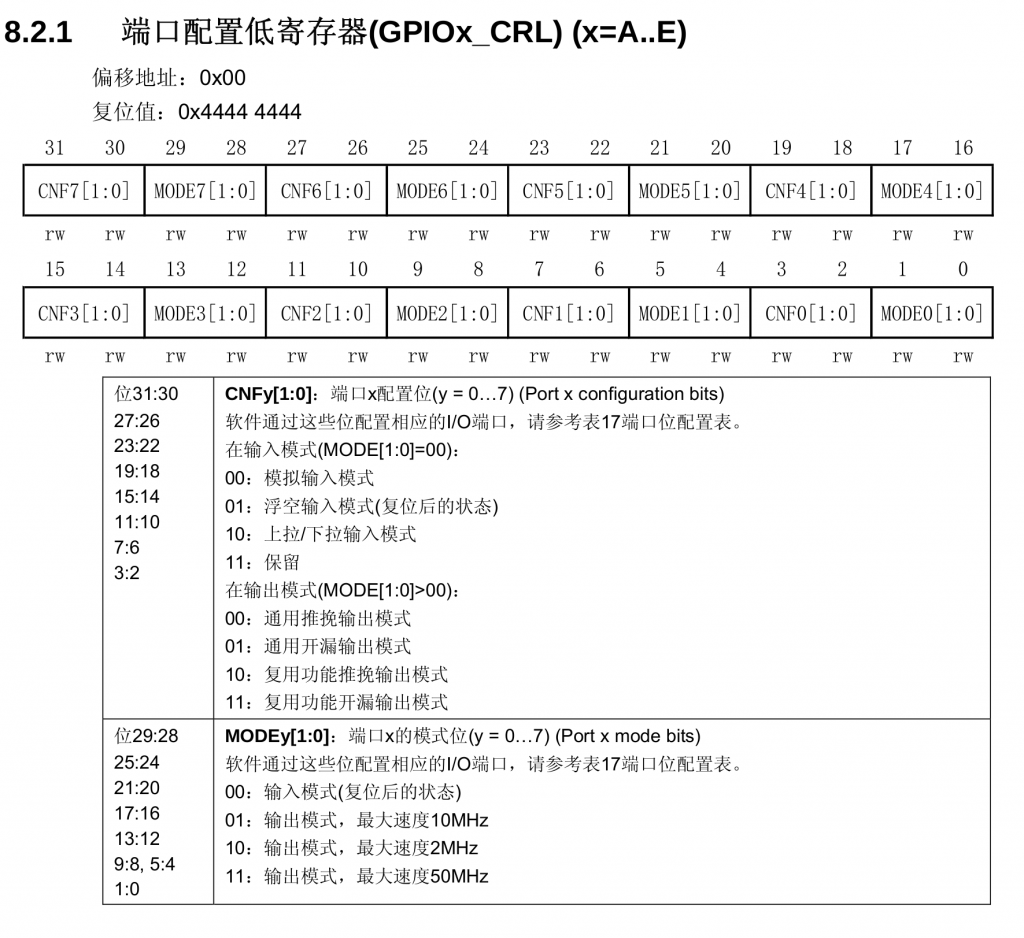

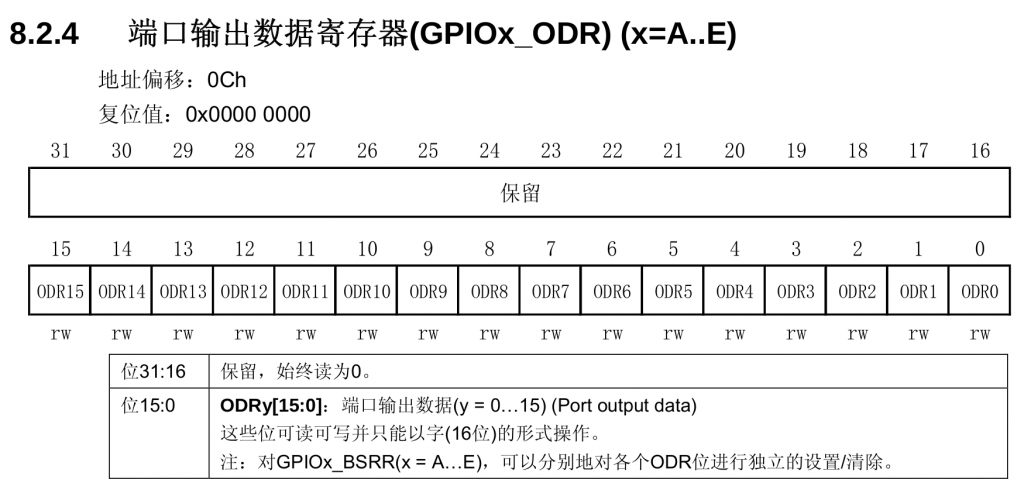

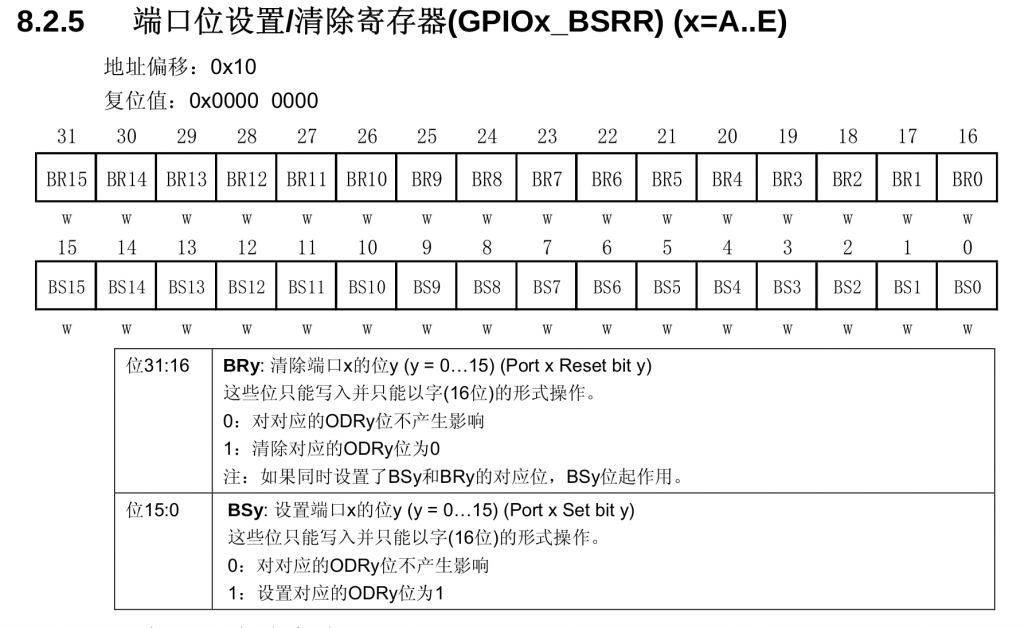

每个GPI/O端口有

两个32位配置寄存器(GPIOx_CRL,GPIOx_CRH),

两个32位数据寄存器(GPIOx_IDR和GPIOx_ODR),

一个32位置位/复位寄存器(GPIOx_BSRR),

一个16位复位寄存器(GPIOx_BRR)

一个32位锁定寄存器(GPIOx_LCKR)。

每个I/O端口位可以自由编程,然而必须按照32位字访问I/O端口寄存器(不允许半字或字节访

问)。GPIOx_BSRR和GPIOx_BRR寄存器允许对任何GPIO寄存器进行读/更改的独立访问;这

样,在读和更改访问之间产生IRQ时不会发生危险。

几种配置GPIO的分析

RCC->APB2ENR |= RCC_APB2ENR_IOPCEN; //开启 GPIO端口 C 的时钟

GPIOC->CRH=0x33333333; //将 8-15号 GPIO配置成:输出模式,速度50MHz

GPIOC->ODR ^= (1 << 13) // 13号 GPIO输出 高电平

// I/O port C clock enable

RCC->APB2ENR = RCC_APB2ENR_IOPCEN;

// Set PC_12 to output

GPIOC->CRH &= ~(GPIO_CRH_MODE12 | GPIO_CRH_CNF12);

GPIOC->CRH |= GPIO_CRH_MODE12;

while(1)

{

GPIOC->BSRR = (1<<12);

delay();

GPIOC->BRR = (1<<12);

delay();

}

// Enable GPIO port clock

RCC -> APB2ENR |= RCC_APB2ENR_IOPAEN;

// Configure the pins using CRL/CRH GPIO registers

#define GPIO_OUTPUT_2MHz (0b10)

#define GPIO_OUTPUT_PUSH_PULL (0 << 2)

GPIOA -> CRL &= ~(GPIO_CRL_MODE0 | GPIO_CRL_CNF0);

GPIOA -> CRL |= GPIO_OUTPUT_2MHz | GPIO_OUTPUT_PUSH_PULL;

// Manipulate the output

/* to toggle */

GPIOA -> ODR ^= (1 << pinNummer);

/* to set */

GPIOA -> BSRR = (1 << pinNummer);

/* to reset */

GPIOA -> BRR = (1 << pinNummer);

//or

GPIOA -> BSRR = (1 << (pinNummer + 16));

RCC->APB2ENR |= 0x10; //enable GPIOC clock

GPIOC->CRH = (GPIOC->CRH & 0xFF0FFFF) | 0x00100000; //PC13 output pull-push, 10MHz speed

GPIOC-> BSRR = 0x00002000; //pc13=1, leave others unchanged

GPIOC->BSRR = 0x20000000; //pc13=0, 其他不变

GPIOC->BSRR = 0x20002000; //pc13=1, 其他不变,设置时,忽略清除

GPIOC->BRR = 0x2000; //pc13=0, 其他不变

GPIOC->ODR = 0x00002000; //pc13=1,并且其他所有都设置为0

GPIOC->ODR |= 0x00002000; //pc13=1, 其他不变

GPIOC->ODR = 0x00000000; //pc13=0, 其他位也强制为0

GPIOC->ODR &= ~0x00002000; //pc12=0, 其他位不变

RCC->APB2ENR |= RCC_APB2ENR_IOPCEN //enable APB2_clock GPIOC

GPIOC->CRH |= GPIO_CRH_MODE13_1 //PC13 output

GPIOC->CRH &= ~GPIO_CRH_CNF13 //PC13 push pull

RCC->APB2ENR |= RCC_APB2ENR_IOPCEN;

GPIOC->CRH &= ~GPIO_CRH_CNF13;

GPIOC->CRH |= GPIO_CRH_MODE13_0;

GPIOC->BSRR = GPIO_BSRR_BR13;

sleep(1);

GPIOC->BSRR = GPIO_BSRR_BS13;

RCC->APB2ENR |=

GPIOC->CRH &= ~GPIO_CRH_CNF13;

GPIOC->CRH |= GPIO_CRH_MODE13_0; //set C13 as a general purporse push-pull output

GPIOC->BSRR |= GPIO_BSRR_BR13; // set C13 0

soft_delay(5000000);

GPIOC->BSRR |= GPIO_BSRR_BS13;

// I/O port C clock enable

RCC->APB2ENR = RCC_APB2ENR_IOPCEN;

// Set PC_13 to output

GPIOC->CRH &= ~GPIO_CRH_CNF13;

GPIOC->CRH |= GPIO_CRH_MODE13_0;

while(1)

{

GPIOC->BSRR = GPIO_BSRR_BS13; // LED off

delay(500);

GPIOC->BRR = GPIO_BRR_BR13; // LED on

delay(500);

}