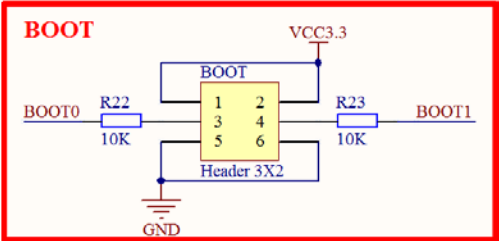

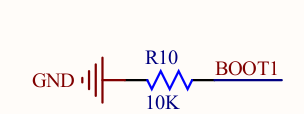

在 STM32F4xx 中,可通过 BOOT[1:0] 引脚选择三种不同的自举模式 boot0 = 0, 主Flash boot0=1, boot1=0 系统存储器 boot0=1, boot1=1 嵌入式SRAM 复位后,在 SYSCLK 的第四个上升沿锁存 BOOT 引脚的值。复位后,用户可以通过设置BOOT1 和 BOOT0 引脚来选择需要的自举模式。BOOT0 为专用引脚,而 BOOT1 则与 GPIO 引脚共用。一旦完成对 BOOT1 的采样,相应GPIO 引脚即进入空闲状态,可用于其它用途。器件退出待机模式时,还会对 BOOT 引脚重新采样。因此,当器件处于待机模式时,这些引脚必须保持所需的自举模式配置。这样的启动延迟结束后,CPU 将从地址 0x0000 0000 获取栈顶值,然后从始于 0x0000 0004 的自举存储器开始执行代码。 注意:

如果器件从 SRAM 自举,在应用程序初始化代码中,需要使用 NVIC 异常及中断向量表和偏移寄存器来重新分配 SRAM 中的向量表。 64 KB CCM (内核耦合存储器)数据 RAM 不属于总线矩阵, 只能通过 CPU 对其进行访问(CPU D总线) 选择自举引脚后,应用程序软件可以将某些存储器设定为从代码空间进行访问(这样,可通过ICode 总线而非系统总线执行代码)。这样的修改通过在 SYSCFG 控制器中编程 SYSCFG 存储器重映射寄存器 (SYSCFG_MEMRMP) 来实现。

- 使用两个位来配置可在地址 0x0000 0000 访问的存储器区域。从而通过软件选择物理重映射,而旁路 BOOT 引脚。

- 这两个位的复位值和复位时 BOOT 引脚的设置相同。当 BOOT 引脚设为 10 [(BOOT1,BOOT0)= (1,0)] 从主 Flash 中自举时,寄存器值为 0x00. 也就是boot引脚的值,被忽略,用寄存器的值代替。

偏移地址:0x00

复位值:0x0000 000X(X 和 BOOT 引脚的设置相同) STM32F4xx 内核集成了串行 /JTAG 调试端口 (SWJ-DP) 默认调试接口是 JTAG 接口。如果调试工具想要切换到 SW-DP, 它必须在 TMS/TCK(分别映射到 SWDIO 和 SWCLK)

上提供专用的 JTAG 序列, 用于禁止 JTAG-DP 并使能 SW-DP。这样便可仅使用 SWCLK和 SWDIO 引脚来激活 SWDP。

该序列为:

- 输出超过 50 个 TCK 周期的 TMS (SWDIO) = 1 信号

- 输出 16 个 TMS (SWDIO) 信号 0111100111100111 (MSB)

- 输出超过 50 个 TCK 周期的 TMS (SWDIO) = 1 信号

脚,可供调试工具立即使用(请注意,除非由调试工具明确编程,否则不分配跟踪输出)。

但是,STM32F4xx MCU 可以禁止部分或全部 SWJ-DP 端口,进而释放相关引脚以用作通

用 IO (GPIO)。 调试时,主机执行以下操作:

注意:

● 在系统复位状态下,分配所有 SWJ 引脚 (JTAG-DP + SW-DP)。

● 在系统复位状态下,调试主机发送 JTAG 序列,以从 JTAG-DP 切换到 SW-DP。

● 仍然在系统复位状态下,调试主机在复位地址处设置断点。

● 释放复位信号,内核停止在复位地址处。

● 从此所有调试通信均使用 SW-DP 完成。然后通过用户软件将其它 JTAG 引脚重新分配为 GPIO。